## BERTScope<sup>™</sup> and BERTScope<sup>™</sup>S Signal Integrity Analyzers

**Technical Specifications**

#### **Benefits:**

- Integrated Signal Integrity Analyzer using the same acquisition circuitry for time, error and jitter domain measurements, to give "same observer" measurements that tie together for faster troubleshooting of your problem devices.

- Unique analysis toolkit gives you unrivaled information quality and depth

- 12.5 Gb/s and 7.5 Gb/s (upgradeable) models will cover your needs as your application bit rates increase

### **Applications:**

- Serial Bus Design

- Semiconductor IC evaluation

- Jitter Tolerance Compliance Testing

- High Speed Backplane Design

- Optical Transceiver Design and Manufacturing

- Recirculating Fiber Loop Experiments

# **BERTScope and BERTScope S** Technical Specifications

#### Contents

| Pattern Generator:       |

|--------------------------|

| Data and Clock Outputs   |

| Ancillary Interfaces     |

| Stressed Eye Option5     |

| Error Detector:          |

| Data and Clock Inputs    |

| Ancillary Interfaces7    |

| User Interfaces8         |

| Parametric Test Options9 |

| Error Analysis10         |

| General Specifications11 |

| Ordering Information12   |

|                          |

7.5 Gb/s (BSA7500A) 12.5 Gb/s (BSA 12500A)

500 Mb/s

**Clock and Clock Outputs**

**Maximum Frequency:**

**Minimum Frequency:**

**Internal Clock**

Input/Output Specifications

Figure 1. Amplitude range.

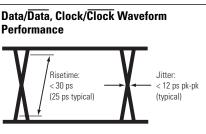

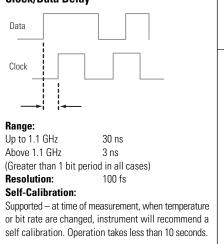

#### Data/Data, Clock/Clock Amplitudes and Offsets **Configuration:** Differential Outputs, each side of pair individually settable for termination,

amplitude, offset.

DC Coupled, 50  $\Omega$ reverse terminated,

APC-3.5 connector. Calibration into 75  $\Omega$

selectable, other

Interface:

Terminations, and Offsets: See Figures 1 and 2

Figure 2. Allowable combinations of termination and offset. Amplitude swings between 0.25 and 2 V allowed; should fit inside shaded area of graph. For example, SCFL uses a 0 V termination, and operates between approximately 0 and -0.9 V; as shown with dotted arrow, it falls within the operating range

> Planar Crown<sup>®</sup> is a registered trademark of Aeroflex/Weinschel, www.aeroflex-weinschel.com

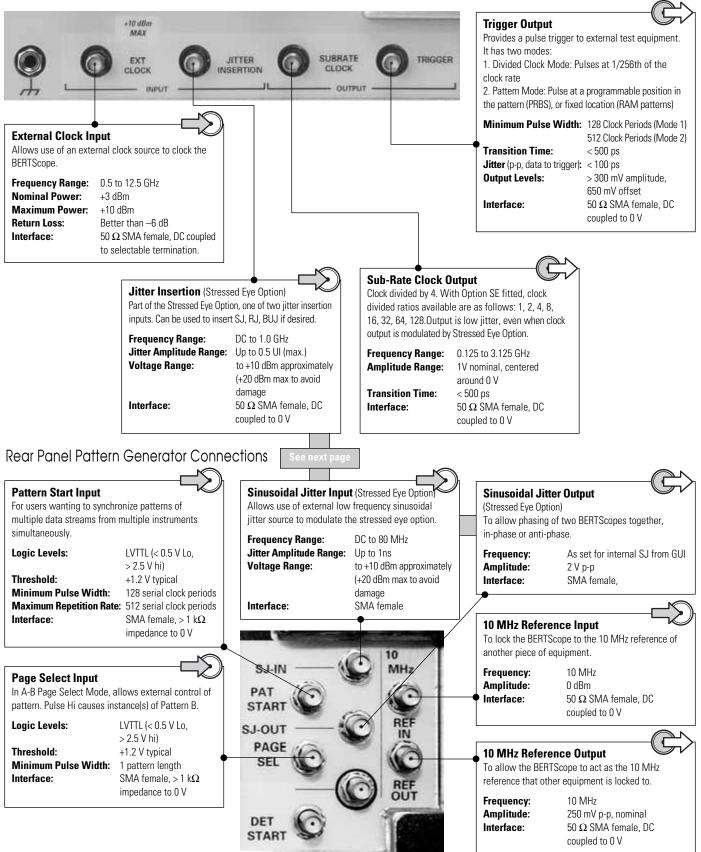

### Pattern Generator Ancillary Connections

Front Panel Pattern Generator Connections

### RIScope

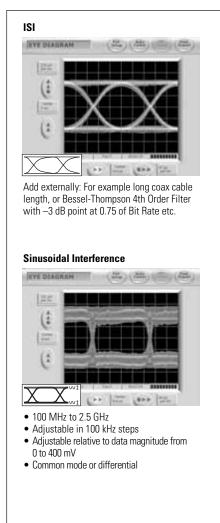

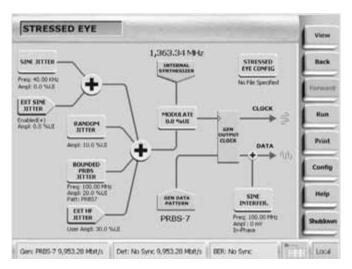

### Pattern Generator Stressed Eye

Generator Option

- Flexible, integrated stressed eye impairment addition to the internal clock

- Easy set-up, with complexity hidden from the user with no loss of flexibility • Verify compliance to multiple standards using the BERTScope and external

- ISI filters. Standards such as: • OIF CEL

- Serial-ATA II PCI-Express

- XFI

- Sinusoidal interference may be inserted in phase or in anti-phase

- Sinusoidal jitter may be locked between two BERTScopes in phase or anti-phase, as required by OIF CEI

#### **Flexible External Jitter Interfaces:**

- Front Panel External High Frequency Jitter Input Connector Jitter from DC to 1.0 GHz up to 0.5 UI (max.) may be added, of any type that keeps with amplitude and frequency boundaries.

- Rear Panel External SJ Low Frequency Jitter Input Connector Jitter from DC to 80 MHz up to 1ns (max) may be added

- Rear Panel SJ Output

#### **Amplitude & ISI Impairments**

#### **Jitter Impairments**

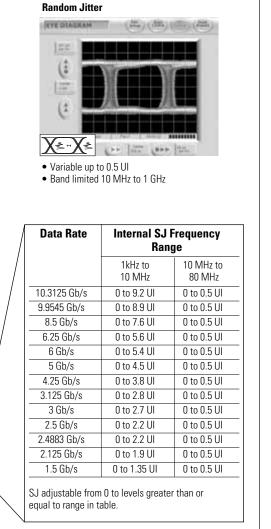

#### Bounded Uncorrelated Jitter

- Variable up to 0.5 UI

- 100 Mb/s to 2.0 Gb/s

- Band limited by selected filters see table below:

| BUJ Rate       | Filter (MHz) |

|----------------|--------------|

| 100 to 499     | 25           |

| 500 to 999     | 50           |

| 1,000 to 1,999 | 100          |

| 2,000          | 200          |

#### **Sinusoidal Jitter**

Notes: Specified for data rates from 1.5 Gb/s to 11.2 Gb/s. Usable with limited performance to 622 Mb/s. Internal RJ, BUJ, and external jitter input limited to 0.5 UI, combined.

## BERTScope" 12.5 Gb/s Signal Analysis

# Error Detector Clock and Data Inputs

| and Data Inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                      | -0                                                                                                                                                                   | Data/Data, Clock I                                | nterfaces                                                                                                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>()</li> <li></li></ul> | Clock Input<br>Maximum Frequency:<br>Minimum Frequency:                                                                                              | 12.5 Gb/s<br>(BSA 12500A & 7500A)<br>500 Mb/s                                                                                                                        | Configuration:<br>Interface:                      | Differential data input.<br>Single-ended clock input,<br>settable for amplitude,<br>offset.<br>APC-3.5 connector.<br>Calibration into 75 Ω                                                          |

| CLOCK 44V MAX<br>INPUT 3V MIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Data and Data Inputs<br>Format:<br>Polarity:<br>Threshold:                                                                                           | NRZ<br>Normal or Inverted<br>Manually adjustable<br>from –2.4 V to +2.5 V,<br>or automatically with<br>Auto-Align                                                    | Preset Logic Families<br>Terminations:            | selectable. Selectable<br>Single-ended, single-ended<br>inverted, differential                                                                                                                      |

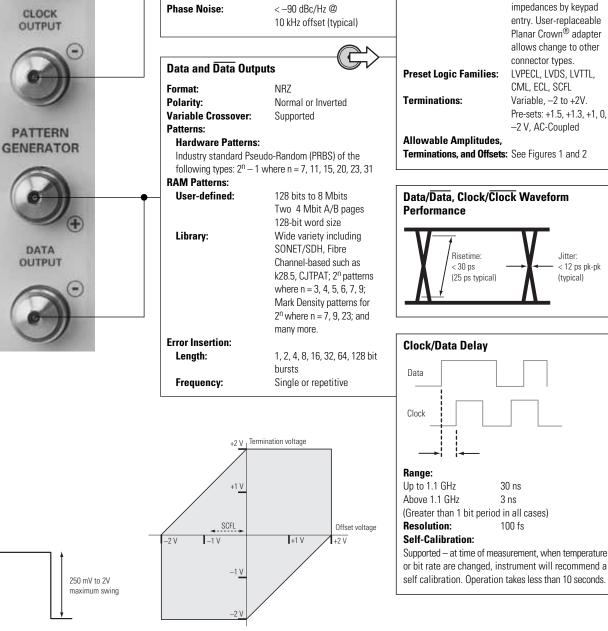

| ERROR<br>DETECTOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Sampling:<br>Sensitivity:<br>Single-Ended<br>Differential:<br>Maximum input<br>Signal Swing:                                                         | Clock rising edge<br>100 mV p-p (typical)<br>50 mV p-p (typical)<br>2 V p-p                                                                                          | Clock/Data Delay                                  |                                                                                                                                                                                                     |

| DATA<br>INPUT<br>JV MIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Patterns:<br>Hardware Patterns:<br>Industry standard Pseudo<br>following types: 2 <sup>n</sup> – 1 who<br>RAM Patterns:<br>User-defined:<br>Library: |                                                                                                                                                                      | or bit rate are changed, self calibration. Operat | 100 fs<br>neasurement, when temperature<br>instrument will recommend a<br>ion takes less than 10 seconds.                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | RAM Pattern Capture:<br>Modes:                                                                                                                       | Capture incoming data up<br>to 8 Mbit in length. Edit<br>captured data, send to<br>Pattern Generator,<br>Error Detector or both.                                     | Auto-Resync:<br>Manual:<br>Pattern Matching:      | User-specified number of<br>128 bit words containing<br>1 or more errors per word<br>initiates a re-sync attempt.<br>User initiates re-sync<br>Error Detector captures specified                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Capture by Length:<br>Capture by Triggers:                                                                                                           | "Detector Start" on rear                                                                                                                                             |                                                   | pattern length and compares<br>next instances to find match.<br>(Fast method, but susceptible<br>to ignoring logical errors.)                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Capture by Length<br>from Trigger:                                                                                                                   | panel goes high, to<br>maximum allowable<br>length or until input<br>goes low.<br>Capture by length initiated<br>from Detector Start input,<br>to pro appoint length |                                                   | Error Detector compares<br>incoming pattern with reference<br>RAM pattern, looks for match, if<br>none found, shifts pattern by one<br>bit and compares again.(Slower<br>but most accurate method.) |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                      | to pre-specified length.                                                                                                                                             |                                                   | BER, Bits Received,<br>Re-Syncs, Measured Pattern<br>Generator and Error<br>Detector clock frequencies                                                                                              |

#### BERTScope" 12.5 Gb/s Signal Analysis

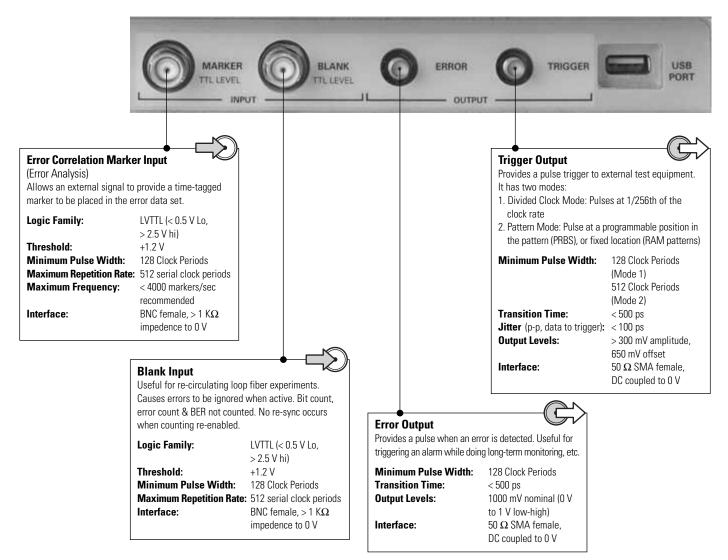

### **Error Detector Ancillary Connections**

Front Panel Error Detector Connections

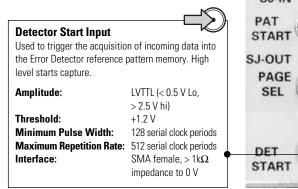

### Rear Panel Error Detector Connections

#### BERTScope 12.5 Gb/s Signal Analysis

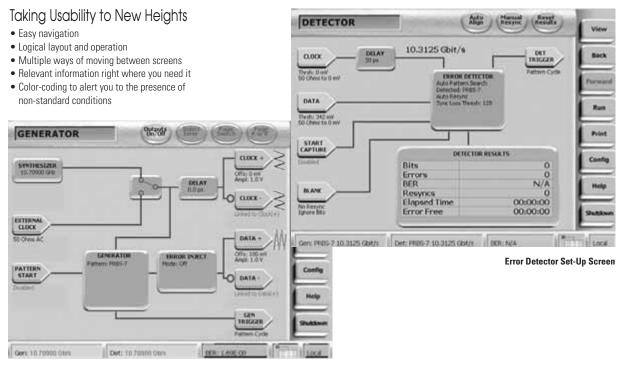

### User Interfaces

#### Pattern Generator Set-Up Screen

#### **Editor Screen**

- Used for pattern editing of standard and AB Page Select patterns, also mask editing

- Views in Binary, Decimal or Hexadecimal

- Support for variable assignments, repeat loops, seeding of PRBS patterns

- Capture and editing of incoming data for example, to make a repeating pattern out of real-world traffic.

#### BERTScope Built-In Parametric Measurements

All BERTScopes come with Eye Diagrams and Mask Test capabilities as standard, along with Error Analysis.

#### Eye Diagram

- 280x350 pixel waveform display

- Deep acquisition

- Automatic Measurements include:

- Rise Time

- Fall Time

- Unit Interval (Data, and also Clock)

- Eye Amplitude

- Noise Level of 1 or 0

- Eye Width

- Eye Height

- Eye Jitter (p-p and RMS)

0 Level, 1 Level

- Extinction Ratio

- Vertical Eye Closure Penalty (VECP)

- Dark Calibration

- Signal to Noise Ratio

- Vp-p, Vmax, Vmin, Crossing Levels

#### Mask Testing

- Library of standard masks e.g. XFP, or edit custom masks

- Addition of positive or negative mask margin

- Import of measured BER Contour to become process control mask

- At least 1000x the sample depth of traditional sampling oscilloscope masks is ideal for ensuring the absence of rare event phenomena.

### **Physical Layer Test Option**

#### **BER Contour Testing**

- Executed with same acquisition circuitry as Eye Diagram measurements for maximum correlation

- As-needed delay-calibration for accurate points

- Automatic scaling, one button measurement

- Extrapolates contours from measured data, increasing measurement depth with run-time and repeatedly updating curve-fits

- Easy export of fitted data in CSV format

- Contours available from 10<sup>-6</sup> to 10<sup>-16</sup> in decade steps

#### Jitter Measurements

- Testing to T11.2 MJSQ BERTScan methodology (also called 'Bathtub Jitter')

- Deep measurements for quick and accurate extrapolation of Total Jitter at user-specified level, or direct measurement

- Separation of Random and Deterministic components, as defined in MJSQ

- As-needed delay-calibration for accurate points

- Easy export of points in CSV format

- Easy one-button measurement

- User-specified amplitude threshold level, or automatic selection

- $\bullet$  Selectable starting BER to increase accuracy when using long patterns, as defined in MJSQ

#### Q Factor Measurement

- One-button measurement of a vertical cross-section through the middle of the eye.

- Easy visualization of system noise effects

Export of data in CSV format

#### **Compliance** Contour

- Validation of transmitter eye performance to standards such as XFP/XFI and OIF CEI.

- Overlay compliance masks onto measured BER contours and easily see whether devices pass the BER performance level specified.

### Live Data Analysis Option

The live data option is designed to measure parametric performance of traffic that is either unknown, or non-repeating. This can include traffic with idle bits inserted such as in systems with clock rate matching. It is also suitable for probing line cards etc.

The option uses one of the two front-end decision circuits to decide whether each bit is a one or zero by placing it in the center of the eye. The other is then used to probe the periphery of the eye to judge parametric performance. This method is powerful for physical layer problems, but will not identify logical problems due to protocol issues, where a zero was sent when it was intended to be a one.

Live data measurements can be made using BER Contour, Jitter Peak, Q Factor. Eye diagram measurements can be made on live data without the use of this option, providing a synchronous clock is available.

The Live Data Analysis option requires the Physical Layer Test Option.

BASIC BER

1

-

Fortial Birlis Fortial Entrop

### **Error Analysis**

Error analysis is a powerful series of views that associate error-occurrences so that underlying patterns can be easily seen. It is easy to focus in on a particular part of an eye diagram, move the sampling point of the BERTScope there, and then probe the pattern sensitivity occurring at that precise location. For example, it is straightforward to examine which patterns are responsible for late or early edges.

Many views come standard with the BERTScope family.

#### **Analysis Views**

- Error Statistics: A tabular display of bit and burst error counts and rates.

- Strip Chart: A strip chart graph of bit and burst error rates.

- Burst Length: A histogram of the number of occurrences of errors of different lengths.

- Error Free Interval: A histogram of the number of occurrences of different error free intervals.

- Correlation: A histogram showing how error locations correlate to user-set block sizes or external Marker signal inputs.

- Pattern Sensitivity: A histogram of the number of errors at each position of the bit sequence used as the test pattern.

- Block Errors: A histogram showing the number of occurrences of data intervals (of a user-set block size) with varying numbers of errors in them.

#### **Error Location Capture**

Live Analysis Error Logging Capacity Error Events/Second Maximum Burst Length Continuous Max. 2 GB file size 10,000 32 kbits

### **Error Analysis Options**

#### Forward Error Correction Emulation

Because of the patented error location ability of the BERTScope, it knows exactly where each error occurs during a test. By emulating the memory blocks typical of block error correcting codes such as Reed-Solomon architectures, bit error rate data from uncorrected data channels can be passed through hypothetical error correctors to find out what a proposed FEC approach would yield. Users can set up error correction strengths, interleave depths, and erasure capabilities to match popular hardware correction architectures.

| Kampet Setural                                                                                               | TITAL ACCUMANTER                             | Personality                | 1    |

|--------------------------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------|------|

| Total Accordings                                                                                             | Autors (11)                                  | After HIC 1                |      |

| form Cauld                                                                                                   | 71.724                                       | 10 100                     | 100  |

| True Adia                                                                                                    | 10000                                        | 114.0                      | 100  |

| 10 Lase                                                                                                      | 10.001 BALINE                                | 9.01123.24                 |      |

| fide Bats                                                                                                    | 1 2 M 10 10 10 10 10 10 10 10 10 10 10 10 10 | 1.1.000.00100.000          | 10.0 |

| inner Cado Tatus Dischel<br>Inner Cado Tatus Dischel<br>Inner Cado Datus Dischel<br>Inner Cado Datus Dischel | Foleyn<br>4.44                               | Circulture<br>(Circulture) |      |

|                                                                                                              |                                              | - Internet                 |      |

#### 2-D Error Mapping

This analysis creates a two-dimensional image of error locations from errors found during the test. Error mapping based on packet size or multiplexer width can show if errors are more prone to particular locations in the packet or particular bits in the parallel bus connected to the multiplexer. This visual tool allows for human eye correlation, which can often illuminate error correlations that are otherwise very difficult to find-even with all the other error analysis techniques.

Error Statistics View showing link performance in terms of bit and burst occurrences 10,017,399,00 ny-fairst Rotated Bit Error Kale (BCR) ant Polated 487-1

14

(49)

Viewing bit and burst error performance over time. This can useful while temperature cycling as part of troubleshooting, for example.

....

Pattern Sensitivity is a powerful way of examining whether error events are pattern related. It shows which pattern sequences are the most problematic, and operates on PRBS and user-defined patterns

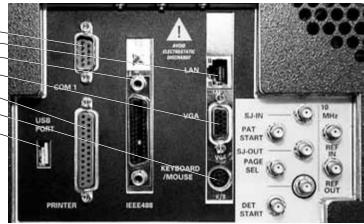

### Scope

### General

#### **PC-Related**: Display:

- **Touch Sensor:** Processor:

- Hard Disk: DRAM: **Operating System: Remote Control:**

- TFT Touch Screen 640 x 480 VGA Analog Resistive 1 GHz Pentium or equivalent 20 GB or greater 256 MB Windows 2000 IEEE-488 (GPIB) or TCP/IP

#### **Supported Interfaces:**

Serial (RS-232) Network (100 Base-T RJ-45 Ethernet) IEEE-488 (GPIB) Monitor (DB-15 VGA) Printer Port (Centronix) Keyboard (Micro) Mouse (PS/2) USB 1.0 (1 front panel, 1 rear panel)

#### **Physical:**

| Power:      |

|-------------|

| Voltage:    |

| Weight:     |

| Dimensions: |

**Environmental:** Warm-up time: Operating **Temperature Range:**

**Humidity**:

**Certifications:**

Support:

#### Period:

Coverage:

#### 1 year (extendable to 3 years with orderable option) Hardware repair or replacement, at SyntheSys Research's discretion. Also covers software updates. Repairs performed at the Menlo Park, California, USA facility. **Calibration interval** 1 year

< 400 Watts

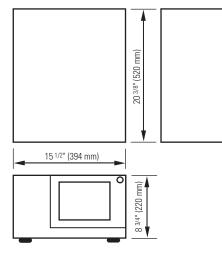

55 lbs (25 kg)  $8\,{}^{3}\!/_{4}{}^{\prime\prime}$  (H) x  $15\,{}^{1}\!/_{2}{}^{\prime\prime}$  (W)

x 20 <sup>3</sup>/<sub>8</sub>" (D)

20 minutes

10 to 40 °C

Non-condensing at 40 °C, 15 to 95%

EU EMC Directive

(CE-Marked) UL: Underwriters Labs (US) certification

CSA (Canada) FCC

90 to 240 V AC, 50 to 60 Hz

### **Ordering Information**

#### **BERTScope 7500A**

7.5 G Pattern Generator, Error Detector, 500 MHz to 7.5 GHz Clock Source, BitAlyzer Error Location Analysis, Eye Diagram Analysis, Mask Test. Upgradeable to BSA12500A for additional charge.

#### **BERTScope 12500A**

12.5 G Pattern Generator, Error Detector, Error Location Analysis, 500 MHz to 12.5 GHz Clock Source, BitAlyzer Error Location Analysis, Eye Diagram Analysis, and Mask Test.

#### BERTScope 12500A, 7500A Stress Analyzer

Powerful stress testing and analysis bundle. Combines Stressed Eye generation (Option SE), Physical Layer Test Suite (Option PL), Error Mapping (Option MAP) and Forward Error Correction (Option FEC) into one convenient and economic bundle.

#### NOTES

Rise times are measured 20% to 80%. Specifications are following a 20 minute warm up period. Specifications subject to charge.

#### Options:

#### BSA7500/12500PL

Physical Layer Test Suite Option including: BER Contour, Q-Factor, Jitter Peak, and Compliance Contour.

#### BSA7500/12500LDA

Enables measurement of Jitter Peak, BER contour and Q-factor on non-repetitive data such as live traffic and system level traffic with inserted idle bits or added protocol. Requires Physical Layer Test option.

#### BSA7500/12500SE

Stressed Eye Option. Clock source with calibrated sinusoidal jitter injection for telecom and datacom jitter tolerance testing, together with bounded, uncorrelated jitter and random jitter injection for stressed eye generation.

#### BSA7500/12500FEC

Forward Error Correction Emulation Option

#### BSA7500/12500MAP

Error Mapping Analysis Option

#### BSA12500RACK

Rack Mounting Kit. For applications that require it, the BSA12500A can be conveniently rack-mounted. The attractive brushed-aluminum rack-mount kit includes slides so that the unit can easily be pulled out from the rack. Additionally, there is an access panel below the front of the unit that can be removed to allow convenient cabling access from inside the rack.

#### BSA12500A3YR

Add 2 Years to Standard 1-Year Warranty. The Extended Warranty option adds a two-year extension to the standard one-year product warranty. All warranties include both hardware repair and software updates. System repair or replacement is at SyntheSys Research's discretion. All repairs are performed at our Menlo Park facility. The warranty includes the cost of ground freight for return shipment. Extended warranties must be ordered within one year of initial delivery.

## BERTScope<sup>™</sup> 12.5 Gb/s Signal Analysis

#### www.bertscope.com

#### **ACCOMPANYING LITERATURE**

BERTScope<sup>™</sup> Family, brochure, literature number SR-DS013

BERTScope™ Clock Recovery Unit CRU 12500A, brochure and technical specifications, literature number SR-DS016

#### THE COMPANY

Founded in 1989, SyntheSys Research, Inc. is a manufacturer of test instruments for analyzing a variety of digital communications channels. From fiber optics to satellites, hard disks to laser communications, and HDTV to digital television, the company has pioneered innovative techniques into award winning, user-friendly instruments. SyntheSys Research is driven by the goal of creating quality products needed by industry professionals.

3475-D Edison Way Menlo Park, CA 94025 U.S.A. Voice 650 364-1853 Fax 650 364-5716 info@synthesysresearch.com www.synthesysresearch.com

BERTScope, BitAlyzer, and Error Location Analysis are trademarks of SyntheSys Research, Incorporated. U.S. and International patents granted and pending. Windows is a registered trademark of Microsoft Corporation.

Copyright © 2005 SyntheSys Research, Inc. All rights reserved. Printed in USA. Specifications subject to change.

SR-DS014 13JUN--05